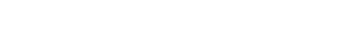

Overview

Modern society is witnessing a sea change in ubiquitous computing, where people have embraced a slew of computing systems as an indispensable part of day-to-day existence. The BRIDGE lab investigates novel system design paradigms to solve many of future problems faced by our semiconductor processing systems. The collaborative research projects span across multiple cross-disciplinary topics including: Artificial Intelligence (AI) Hardware, AI Hardware Security, Low Power Edge computing hardware, and design of Secure, Reliable and Energy Efficient processors and accelerators.

Selected Recent Publications

- DAC-23: Noel Daniel, Zinnia Muntaha Mowri, Andrew Chamberlin, Sanghamitra Roy and Koushik Chakraborty, "STRIVE: Enabling Choke Point Detection and Timing Error Resilience in a Low-Power Tensor Processing Unit", Proceedings of the 60th Design Automation Conference, July 9-13, 2023, San Francisco, CA, USA (ACCEPTED)

- DAC-21: Pramesh Pandey, Noel Daniel, Sanghamitra Roy and Koushik Chakraborty, "UPTPU: Improving Energy

Efficiency of a Tensor Processing Unit through Underutilization Based Power-Gating", Proceedings of the 58th Design Automation Conference, December 5-9, 2021, San Francisco, CA, USA - ASPDAC-20: Noel Daniel, Tahmoures Shabanian, Prabal Basu, Pramesh Pandey, Koushik Chakraborty, Sanghamitra Roy and Zhen Zhang "EFFORT: Enhancing Energy Efficiency and Error Resilience of a Near-Threshold Tensor ProcessingUnit", Asia and South Pacific Design Automation Conference (ASPDAC)

- TVLSI-19: Sourav Sanyal, Prabal Basu, Aatreyi Bal, Sanghamitra Roy and Koushik Chakraborty “Exploring Warp Criticality in Near-Threshold GPGPU Applications using a Dynamic Choke Point Analysis”, IEEE Transactions on Very Large Scale Integration Systems (TVLSI)

- DAC-19: Pramesh Pandey, Prabal Basu, Koushik Chakraborty, Sanghamitra Roy, "GreenTPU: Improving Timing Error Resilience of a Near-Threshold Tensor Processing Unit", Design Automation Conference, June 2-6, 2019 Las Vegas, NV, USA.

- TVLSI-18: Aatreyi Bal, Sanghamitra Roy, and Koushik Chakraborty, "Trident: Comprehensive Choke Error Mitigation in NTC Systems", IEEE Transactions on Very Large Scale Integration Systems, 2018

- ISLPED-18: Tahmoures Shabanian, Aatreyi Bal, Prabal Basu, Koushik Chakraborty, Sanghamitra Roy, "ACE-GPU: Tackling Choke Point Induced Performance Bottlenecks in a Near-Threshold Computing GPU", International Symposium on Low Power Electronics and Design, July 23–25, 2018, Seattle,WA, USA.

- ISLPED-18: Pramesh Pandey, Asmita Pal, Koushik Chakraborty, Sanghamitra Roy, "Reliability and Uniformity Enhancement in 8T-SRAM based PUFs operating at NTC. ", International Symposium on Low Power Electronics and Design, July 23–25, 2018, Seattle,WA, USA.

- TETC-18: Prabal Basu, Pramesh Pandey, Aatreyi Bal, Chidhambaranathan Rajamanikkam,Koushik Chakraborty, Sanghamitra Roy, "TITAN: Uncovering the Paradigm Shift in Security Vulnerability at Near-Threshold Computing",IEEE Transactions on Emerging Topics in Computing, January 2018

- DATE-18: Aatreyi Bal, Sanghamitra Roy, and Koushik Chakraborty,"Trident: A Comprehensive Timing Error Resilient Technique against Choke Points at NTC",Proceedings of theIEEE/ACM Design Automation and Test in Europe, March 2018 (Won Best Paper Nomination)

- ESL-17 :Prabal Basu,Chidhambaranathan R, Aatreyi Bal, Pramesh Pandey,Trevor Carter,Koushik Chakraborty and Sanghamitra Roy,"FIFA: Exploring a Focally Induced Fault Attack Strategy in Near-Threshold Computing",IEEE Embedded Systems Letters, 2017

- TVLSI-17:Aatreyi Bal, Shamik Saha,Sanghamitra Roy, and Koushik Chakraborty,"Dynamic Choke Sensing for Timing Error Resilience in NTC Systems."IEEE Transactions on Very Large Scale Integration (VLSI) Systems, October2017

- TVLSI-17:Prabal Basu, Rajesh JayashankaraShridevi, Koushik Chakraborty and Sanghamitra Roy,"IcoNoClast: Tackling Voltage Noise in the NoC Power Supply Through Flow-Control and Routing Algorithms",IEEE Transactions on Very Large Scale Integration Systems, 2017

- DATE-17:Aatreyi Bal, Shamik Saha, Sanghamitra Roy, and Koushik Chakraborty, “Revamping Timing Error Resilience to Tackle Choke Pointsat NTCSystems,”Proceedings of the IEEE/ACM Design Automation and Test in Europe, March 2017, Lausanne, Switzerland.

- TODAES-17: Shamik Saha, Prabal Basu, Chidhambaranathan R, Aatreyi Bal, Koushik Chakraborty, and Sanghamitra Roy, "SSAGA: SMs Synthesized for Asymmetric GPGPU Applications", ACM Transactions on Design Automation of Electronic Systems.

- ICCAD-16:Chidhambaranathan R,Rajesh JayashankaraShridevi,Sanghamitra Roy, and Koushik Chakraborty, "BoostNoC: Power Efficient Network-on-Chip Architecture for Near Threshold Computing", IEEE/ACM International Conference on Computer-aided Design, November 2016, Austin, Texas.

- DAC-16: Prabal Basu,Hu Chen,Shamik Saha, Koushik Chakraborty, and Sanghamitra Roy, "SwiftGPU: Fostering Energy Efficiency in a Near-Threshold GPU Through Tactical Performance Boost", Proceedings of the 53rd IEEE/ACM Design Automation Conference, June 2016, Austin, Texas.

- DAC-16: Rajesh JayashankaraShridevi, Chidhambaranathan R,Sanghamitra Roy, and Koushik Chakraborty, "Catching the Flu: Emerging threats from a Third Party Power Management Unit", Proceedings of the 53rd IEEE/ACM Design Automation Conference, June 2016, Austin, Texas. accepted for publication.

- DAC-16: Atif Yasin,Jeff Zhun, Siddharth Garg, Hu Chen,Sanghamitra Roy, and Koushik Chakraborty, "Synergistic Timing Speculation for Multi-threaded Programs", Proceedings of the 53rd IEEE/ACM Design Automation Conference, June 2016, Austin, Texas, accepted for publication.

- DATE-16: Prabal Basu, Rajesh JayashankaraShridevi, Koushik Chakraborty and Sanghamitra Roy, "PRADA: Combating Voltage Noise in the NoC Power Supply Through Flow-Control and Routing Algorithms", Proceedings of the IEEE/ACM Design Automation and Test in Europe, March 2016, Dresden, Germany (Accepted for publication).

- ISLPED-15: Rajesh JayashankaraShridevi, Dean Michael Ancajas, Koushik Chakraborty and Sanghamitra Roy, "Tackling Voltage Emergencies in NoC Through Timing Error Resilience", Proceedings of the IEEE International Symposium on Low Power Electronics and Design, July 2015, Rome, Italy, accepted for publication (Acceptance Rate 18.2%).

- DAC-15: Hu Chen, Dieudonne Manzi, Sanghamitra Roy and Koushik Chakraborty, "Opportunistic Turbo Execution in NTC: Exploiting the Paradigm Shift in Performance Bottlenecks", Proceedings of the 52nd IEEE/ACM Design Automation Conference, June 2015, San Francisco, CA, accepted for publication.

- CODES+ISSS-14: Dean Michael Ancajas, Koushik Chakraborty and Sanghamitra Roy, "Tackling QoS-induced Aging in Exascale Systems through Agile Path Selection", IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (Nomination for Best Paper Award).

- Robust L1 Cache Design.", IEEE/ACM International Symposium on Quality Electronic Design (Accepted).

- DAC-14: Dean Michael Ancajas, Koushik Chakraborty and Sanghamitra Roy, "Fort-NoCs: Mitigating the Threat of a Compromised-NoC", IEEE/ACM 51st Design Automation Conference (Accepted).

- DATE-14:Hu Chen, Sanghamitra Roy, and Koushik Chakraborty, "DARP: Dynamically Adaptable Resilient Pipeline Design in Microprocessors", IEEE/ACM Design Automation and Test in Europe. March 2014. Dresden, Germany.

- DAC-13:Koushik Chakraborty, Brennan Cozzens, Sanghamitra Roy, and Dean Michael Ancajas, "Efficiently Tolerating Timing Violations in Pipelined Microprocessors", IEEE/ACM 50th Design Automation Conference (Accepted). June 2013, Austin, Texas

- DAC-13: Dean Michael Ancajas, James McCabe Nickerson, Koushik Chakraborty, and Sanghamitra Roy, "HCI Tolerant NoC Router Micro-architecture", IEEE/ACM 50th Design Automation Conference (Accepted).June 2013, Austin, Texas

- DAC-13: Dean Michael Ancajas, Koushik Chakraborty, and Sanghamitra Roy, "DMR3D: Dynamic Memory Relocation in 3D Multicore Systems", IEEE/ACM 50th Design Automation Conference (Accepted). June 2013, Austin, Texas

- DATE-13:Dean Michael Ancajas, Koushik Chakraborty, and Sanghamitra Roy, "Proactive Aging Management in Heterogeneous NoCs through a Criticality-Driven Routing Approach", IEEE/ACM Design Automation and Test in Europe (Accepted)